SEGGER Evaluation Software for RISC-V Architecture

SEGGER provides board support packages (BSPs) and complete projects, available for various Evaluation boards. Different software packages are available for different boards.

Some packages are executable demos which can not be modified; some packages are versions for evaluation purposes which come with the software in a library and the application in source code form, as well as a project for the IDE that has been used.

Versions for evaluation purposes can usually be recompiled easily in less than a minute if the required compiler and IDE is installed. The application program can be modified, allowing intensive tests of the software. emWin versions for evaluation purposes usually also contain a simulation environment which allows test and recompilation on a PC.

Below is a list of supported Evaluation boards. The software can easily be ported to other hardware platforms. If you are looking for software for an Evaluation board not in this list, please get in touch with us at info@segger.com.

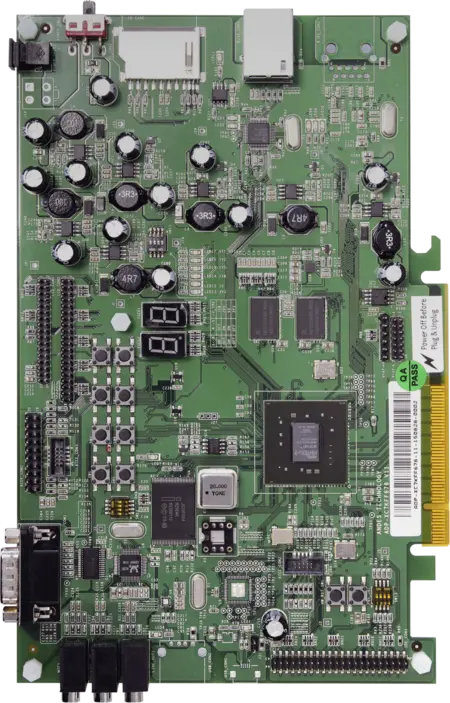

Andes Technology ADP-XC7K160

SEGGER Evaluation Software

Included components:

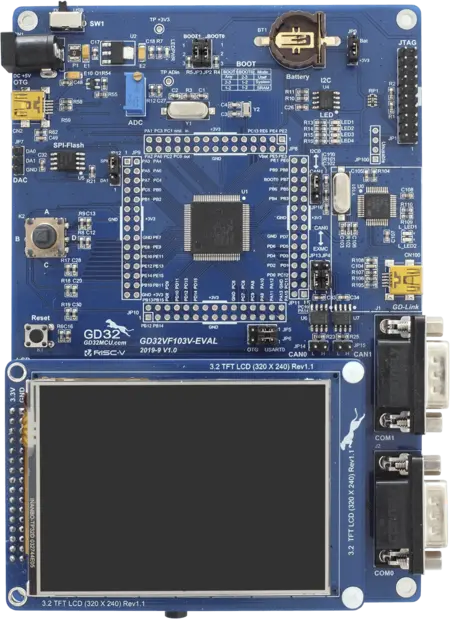

GigaDevice GD32VF103 Eval

SEGGER Evaluation Software

Included components:

| Product | Supported features |

|---|---|

BASE + AntiAliasing, Bitmap Converter, Font Converter, Memory Devices, Simulation, Widgets, Window Manager, GUIDRV_FlexColor |

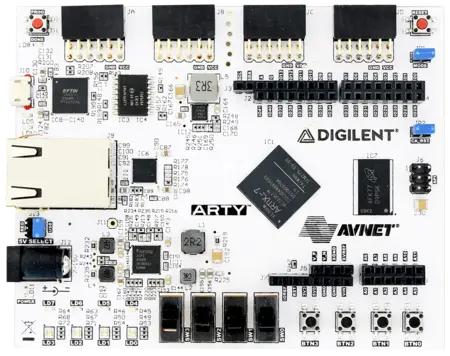

RISC-V Digilent ARTY

The Arty A7-35T FPGA Development Board is an FPGA board, that can host a bitstream to become a RISC-V processor. The below examples are based on the SiFive E31 bitstreams, that are available as a test version from SiFive's web page.