# J-Link-OB-SAM3U128

User guide of the onboard debug probe based on AT91SAM3U128 MCU

Document: UM08018 Revision: 6

Date: January 18, 2018

A product of SEGGER Microcontroller GmbH

www.segger.com

### **Disclaimer**

Specifications written in this document are believed to be accurate, but are not guaranteed to be entirely free of error. The information in this manual is subject to change for functional or performance improvements without notice. Please make sure your manual is the latest edition. While the information herein is assumed to be accurate, SEGGER Microcontroller GmbH (SEGGER) assumes no responsibility for any errors or omissions. SEGGER makes and you receive no warranties or conditions, express, implied, statutory or in any communication with you. SEGGER specifically disclaims any implied warranty of merchantability or fitness for a particular purpose.

## Copyright notice

You may not extract portions of this manual or modify the PDF file in any way without the prior written permission of SEGGER. The software described in this document is furnished under a license and may only be used or copied in accordance with the terms of such a license.

© 2004-2017 SEGGER Microcontroller GmbH, Hilden / Germany

### **Trademarks**

Names mentioned in this manual may be trademarks of their respective companies.

Brand and product names are trademarks or registered trademarks of their respective holders.

### **Contact address**

SEGGER Microcontroller GmbH

In den Weiden 11 D-40721 Hilden

### Germany

Tel. +49 2103-2878-0 Fax. +49 2103-2878-28 E-mail: support@segger.com Internet: www.segger.com

## **Manual versions**

This manual describes the current version. If you find an error in the manual, please report it to us and we will try to assist you as soon as possible.

Contact us for further information on topics that are not yet documented.

Print date: January 18, 2018

| Manual version | Revision | Date   | Ву | Description                                                    |

|----------------|----------|--------|----|----------------------------------------------------------------|

| 0.00           | 6        | 171012 | NG | Initial reworked Version                                       |

| 0.00           | 5        | 160317 | AG | "Software UART via J-Link API" removed.                        |

| 0.00           | 4        | 160315 | NG | Fixed a typo in Chapter "FAQ"                                  |

| 0.00           | 3        | 160209 | AG | Chapter "Introduction" *Section "Supported CPU cores" updated. |

| 0.00           | 2        | 140528 | AG | Chapter "Schematics" updated.                                  |

| 0.00           | 1        | 130508 | AG | Chapter "Schematics" updated.                                  |

| 0.00           | 0        | 111122 | EL | Initial Version                                                |

## **About this document**

## **Assumptions**

This document assumes that you already have a solid knowledge of the following:

- The software tools used for building your application (assembler, linker, C compiler).

- The C programming language.

- The target processor.

- DOS command line.

If you feel that your knowledge of C is not sufficient, we recommend *The C Programming Language* by Kernighan and Richie (ISBN 0-13-1103628), which describes the standard in C programming and, in newer editions, also covers the ANSI C standard.

### How to use this manual

This manual explains all the functions and macros that the product offers. It assumes you have a working knowledge of the C language. Knowledge of assembly programming is not required.

## Typographic conventions for syntax

This manual uses the following typographic conventions:

| Style          | Used for                                                                                                                 |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------|--|

| Body           | Body text.                                                                                                               |  |

| Keyword        | Text that you enter at the command prompt or that appears on the display (that is system functions, file- or pathnames). |  |

| Parameter      | Parameters in API functions.                                                                                             |  |

| Sample         | Sample code in program examples.                                                                                         |  |

| Sample comment | Comments in program examples.                                                                                            |  |

| Reference      | Reference to chapters, sections, tables and figures or other documents.                                                  |  |

| GUIElement     | Buttons, dialog boxes, menu names, menu commands.                                                                        |  |

| Emphasis       | Very important sections.                                                                                                 |  |

## **Table of contents**

| 1 | Why J-Link OB?                                                                                         | 8              |

|---|--------------------------------------------------------------------------------------------------------|----------------|

| 2 | Supported target CPU cores                                                                             | 9              |

| 3 | Supported target interfaces                                                                            | 10             |

|   | 3.1 Target interface pins 3.2 Target interface JTAG 3.3 Target interface SWD 3.4 Target interface VCOM | 11<br>12<br>13 |

| 4 | Compatible MCUs as J-Link OB host                                                                      | 15             |

| 5 | Schematics                                                                                             | 16             |

| 6 | Glossary                                                                                               | 17             |

## Why J-Link OB?

The J-Link on-board (J-Link OB) was designed in order to provide a low-cost, space-saving and on-board alternative to the general J-Link, for eval board manufacturers. J-Link OB can be used with the same software package as the general J-Links and can be used with the same utilities (as far as the feature set of the J-Link OB supports this)

#### Note

It is not allowed to use J-Link-OB-SAM3U128 for stand-alone emulators.

## Supported target CPU cores

For a list of cores supported by this J-Link OB model, please refer to here: *J-Link OB Model overview*

## Supported target interfaces

The J-Link-OB-SAM3U128 supports the following target interfaces:

- JTAG

- SWD (+ SWO)

It may therefore be used for ARM7/9 target CPUs or other target CPUs with JTAG connection or Cortex-M targets with JTAG or Serial Wire Debug connection.

## 3.1 Target interface pins

The J-Link-OB-SAM3U128 provides the following target interface signals:

| Signal    | Signal Out Pin | Signal In Pin |

|-----------|----------------|---------------|

| TCK/SWCLK | PA17 / Pin 14  | PA22 / Pin 5  |

| TMS/SWDIO | PA18 / Pin 17  | PA15 / Pin 12 |

| TDI       | PA20 / Pin 19  | PA13 / Pin 10 |

| TDO/SWO   | N/A            | PA21 / Pin 20 |

| #RESET    | PA4 / Pin 30   | PA3 / Pin 29  |

| nTRST     | PA1 / Pin 27   | PA0 / Pin 26  |

| RTCK      | N/A            | PA30 / Pin 6  |

| TXD       | PA12 / Pin 41  | N/A           |

| RXD       | N/A            | PA11 / Pin 40 |

| CTS       | N/A            | PA10 / Pin 39 |

| RTS       | PA9 / Pin 38   | N/A           |

Which signals are required depends on what features shall be supported on the evaluation board. If support for a specific feature or interface is not required, the spare pins should be left open. For more information about which target interface requires which signals, please refer to the following sections.

## 3.2 Target interface JTAG

If JTAG support is required on the target hardware to be designed, the following signals need to be connected:

| Signal | Signal Out Pin | Signal In Pin |

|--------|----------------|---------------|

| TCK    | PA17 / Pin 14  | PA22 / Pin 5  |

| TMS    | PA18 / Pin 17  | PA15 / Pin 12 |

| TDI    | PA20 / Pin 19  | PA13 / Pin 10 |

| TDO    | N/A            | PA21 / Pin 20 |

| #RESET | PA4 / Pin 30   | PA3 / Pin 29  |

| nTRST  | PA1 / Pin 27   | PA0 / Pin 26  |

| RTCK   | N/A            | PA30 / Pin 6  |

### Note

TCK and TMS share functionality with the SWCLK and SWDIO pins used for the SWD interface. So if JTAG connected on the J-Link OB, SWD is supported automatically as well.

## 3.3 Target interface SWD

If SWD (+ optional SWO) support is required on the target hardware to be designed, the following signals need to be connected:

| Signal | Signal Out Pin | Signal In Pin |

|--------|----------------|---------------|

| SWCLK  | PA17 / Pin 14  | PA22 / Pin 5  |

| SWDIO  | PA18 / Pin 17  | PA15 / Pin 12 |

| SWO    | N/A            | PA21 / Pin 20 |

| #RESET | PA4 / Pin 30   | PA3 / Pin 29  |

If SWO support is not required (e.g. when the target CPU is Cortex-M0/M0+ based, which does not provide SWO support), the SWO signal can be left open.

## 3.4 Target interface VCOM

This J-Link OB model can support virtual COM port (VCOM) as an optional and additional target interface. For more information about what VCOM is, please refer to J-Link VCOM functionality .

If VCOM (+ optional hardware flow control) support is required on the target hardware to be designed, the following signals need to be connected:

| Signal | Signal Out Pin | Signal In Pin |

|--------|----------------|---------------|

| TXD    | PA12 / Pin 41  | N/A           |

| RXD    | N/A            | PA11 / Pin 40 |

| CTS    | N/A            | PA10 / Pin 39 |

| RTS    | PA9 / Pin 38   | N/A           |

If hardware flow control support is not required, the CTS and RTS signal can be left open.

# Compatible MCUs as J-Link OB host

The J-Link-OB-SAM3U128 is based on the Atmel AT91SAM3U128 96 MHz, 128 KB flash series MCUs. The following microcontrollers are compatible to this J-Link OB model:

Atmel AT91SAM3U128 LQFP100

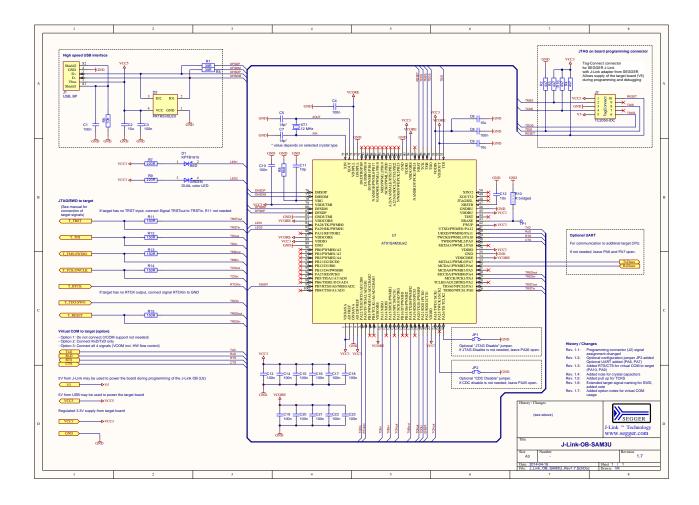

## **Schematics**

## **Glossary**

This chapter describes important terms used throughout this manual.

18 CHAPTER 6

## Adaptive clocking

A technique in which J-Link / J-Trace sends out a clock signal and waits for the returned clock from the target device before generating the next clock pulse. The technique allows the J-Link / J-Trace interface unit to adapt to different signal drive capabilities, different cable lengths and variable target clock speeds. Adaptive clocking can be used when it is supported by the connected target device.

### **RESET**

Abbreviation of System Reset. The electronic signal which causes the target system other than the TAP controller to be reset. This signal is also known as "nSRST" "nSYSRST", "nRST", or "nRESET" in some other manuals. See also nTRST.

### nTRST

Abbreviation of TAP Reset. The electronic signal that causes the target system TAP controller to be reset. This signal is known as nICERST in some other manuals. See also nSRST.

### **RTCK**

Returned TCK. The signal which allows Adaptive Clocking.

### **TCK**

The electronic clock signal which times data on the TAP data lines TMS, TDI, and TDO.

### TDI

The electronic signal input to a TAP controller from the data source (upstream). Usually, the TDI signal of J-Link is connected to the TDI of the first TAP controller in a JTAG chain.

### **TDO**

The electronic signal output from a TAP controller to the data sink (downstream). Usually, the TDO signal of J-Link is connected to the TDO of the last TAP controller in a JTAG chain.

### **TMS**

The electronic signal Test Mode Select is an input to the TAP controller and it is used to select different stages of state machine. It is clocked in into the TAP controller using the TCK signal.(upstream). Usually, the TMS output signal of J-Link is connected to the TMS input of the first TAP controller in a JTAG chain. For Cortex-M CPUs this signal may also be used as the bidirectional data signal SWDIO when the CPU is accessed in serial wire debug mode SWD.

#### **SWD**

A serial communication protocol for Cortex M CPUs which may used for communication with a debug device as an alternative communication channel to JTAG. The SWD communication uses less pins.

### **SWDIO**

The bidirectional electronic signal for communication of a Cortex M CPU accessed in serial wire debug mode. Normally, the TMS input pin of the Cortex M CPU is used as SWDIO pin in serial wire mode.

### **SWCLK**

The electronic signal which times data on the SWDIO data line used in serial wire debug mode. The SWCLK pin is typically the TCK pin used as JTAG clock input, when JTAG is also supported by the device.

19 CHAPTER 6

## **SWO**

The electronic asynchronous signal for trace data output or SWV output data which may be sent by the application on a Cortex-M CPU running in serial wire debug mode. J-Link-OB-SAM3U128 is able to receive the data in asynchronous mode when SWO of the target CPU is connected to the SWOin signal of J-Link-OB-SAM3U128. Normally the SWO output signal of a Cortex-M CPU is directed via the TDO signal pin, but may be separated on some devices.